664293 DP-953

AEC RESEARCH AND DEVELOPMENT REPORT

# SOLID-STATE DC AMPLIFIER WITH HIGH INPUT IMPEDANCE

J. S. Byrd

Savannah River Laboratory

Aiken, South Carolina

#### LEGAL NOTICE

This report was prepared as an account of Government sponsored work. Neither the United States, nor the Commission, nor any person acting on behalf of the Commission:

- A. Makes any warranty or representation, expressed or implied, with respect to the accuracy, completeness, or usefulness of the information contained in this report, or that the use of any information, apparatus, method, or process disclosed in this report may not infringe privately owned rights; or

- B. Assumes any liabilities with respect to the use of, or for damages resulting from the use of any information, apparatus, method, or process disclosed in this report.

As used in the above, "person acting on behalf of the Commission" includes any employee or contractor of the Commission, or employee of such contractor, to the extent that such employee or contractor of the Commission, or employee of such contractor prepares, disseminates, or provides access to, any information pursuant to his employment or contract with the Commission, or his employment with such contractor.

Printed in USA. Price \$1.00

Available from the Clearinghouse for Federal Scientific and Technical Information, National Bureau of Standards, U. S. Department of Commerce, Springfield, Virginia

664293

DP-953

Instruments (TID-4500, 38th Ed.)

### SOLID-STATE DC AMPLIFIER WITH HIGH INPUT IMPEDANCE

bу

Joseph S. Byrd

Approved by

J. L. Crandall, Research Manager Experimental Physics Division

February 1965

E. I. DU PONT DE NEMOURS & COMPANY SAVANNAH RIVER LABORATORY AIKEN, SOUTH CAROLINA

CONTRACT AT(07-2)-1 WITH THE

UNITED STATES ATOMIC ENERGY COMMISSION

#### **ABSTRACT**

A solid-state operational amplifier with a field-effect transistor at the input was designed and tested. The amplifier has an input resistance greater than  $5 \times 10^{11}$  ohms and an input leakage current less than  $10^{-12}$  ampere at room temperature. The amplifier is useful in nuclear instrumentation applications where it is necessary to measure very small signal currents.

#### **CONTENTS**

|                            | Page |  |

|----------------------------|------|--|

| List of Tables and Figures | 4    |  |

| Introduction               |      |  |

| Summary                    | 5    |  |

| Discussion                 | 6    |  |

| Preliminary Work           | 6    |  |

| FET Input Circuit          |      |  |

| Differential Amplifier     |      |  |

| Operational Amplifier      | 11   |  |

| Future Work                |      |  |

| References                 |      |  |

| Appendix - FET Diagrams    |      |  |

#### LIST OF TABLES AND FIGURES

| <u>Table</u> |                                               | Page |

|--------------|-----------------------------------------------|------|

| I            | Input Capacitance Values                      | 9    |

| II           | Operational Amplifier Specifications          | 12   |

| Figure       |                                               |      |

| 1            | FET Input Circuit - Schematic                 | 7    |

| 2            | Bandwidth Curves - Amplifier Bootstrapped     | 8    |

| 3            | Bandwidth Curves - Amplifier Not Bootstrapped | 8    |

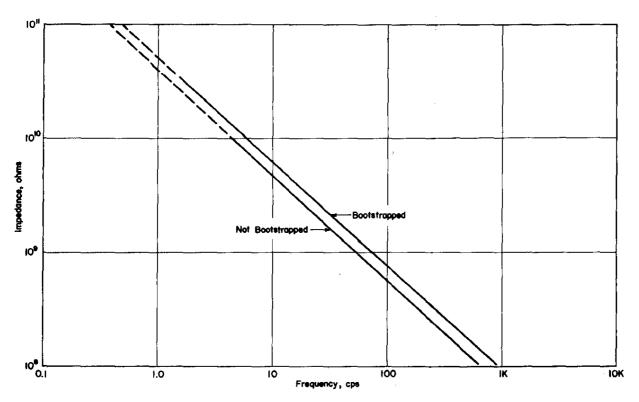

| 4            | Impedance vs. Frequency - FET Input Circuits  | 9    |

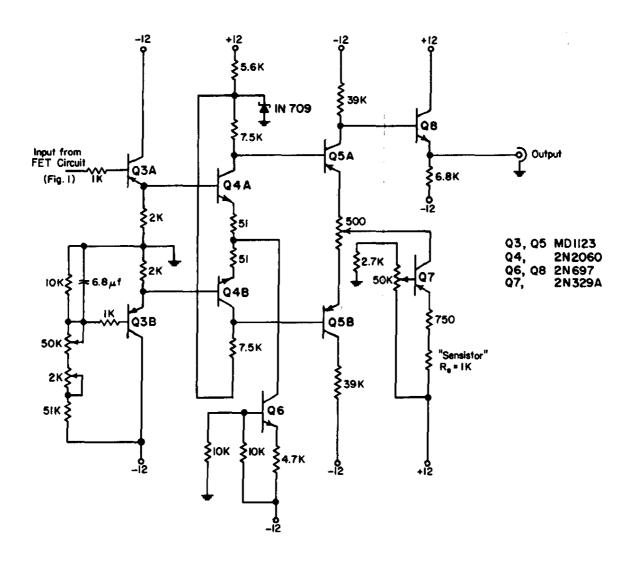

| 5            | Differential Amplifier - Schematic            | 10   |

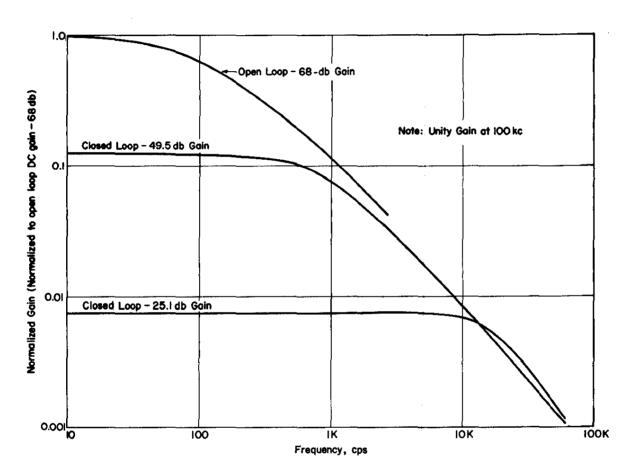

| 6            | Gain-Frequency Curves - Operational Amplifier | 11   |

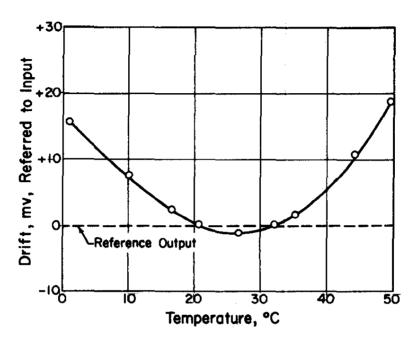

| 7            | Voltage Drift of Operational Amplifier        | 12   |

### SOLID-STATE DC AMPLIFIER WITH HIGH INPUT IMPEDANCE

#### INTRODUCTION

An amplifier with high input impedance is needed in many nuclear instrumentation applications such as electrometers, radiation detection devices, and reactor log n-period systems. For many years electrometer vacuum tubes were the only input elements that could meet this high impedance requirement. However with the development of the field-effect transistor (FET), which has an extremely high input impedance (10<sup>11</sup> - 10<sup>18</sup> ohms), solid-state electronics can now be designed for these applications.

The amplifier described in this report represents an initial step toward improving nuclear measurement and control techniques by using field-effect transistors (FETs) and all solid-state circuitry. A specific application for the amplifier is in a new solid-state log n-period system. The logarithmic amplifier in such a system usually provides on a single scale an indication of neutron flux over a range of seven to eight decades. The usual practice of logarithmic conversion of the signal current from the ion chamber neutron detector has been to use a reverse biased thermionic diode. However diodes generally do not have a logarithmic relationship over more than six to seven decades. Work by Gibbons and Horn of Stanford University (1) has shown that a silicon transistor connected as the feedback element of an operational amplifier can be made to exhibit an accurate logarithmic transfer response over a range of nine decades. It is planned to use the present amplifier for experiments in such circuitry.

#### SUMMARY

A solid-state DC amplifier was designed for use as an operational amplifier. The circuit uses a field-effect transistor (FET) as the input circuit element and differential transistor stages to provide an overall voltage gain of 2400 (68 db). The gain-bandwidth product is 100 kc, and the temperature drift between 20 and 32°C is 1 mv, referred to the input.

Tests on the amplifier showed that good performance can be obtained with an FET at the input. Input characteristics of the circuit are limited only by the parameters of the FET.

#### DISCUSSION

#### Preliminary Work

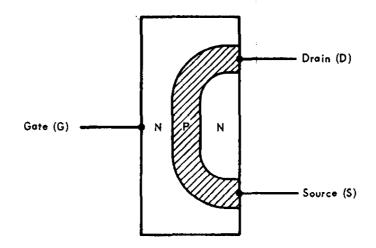

A type SU348 field-effect transistor (FET) was selected for the input circuit on the basis that it had the highest input impedance of any FET available at the time. Laboratory tests were conducted to verify the operating characteristics of the FET, and several circuits were tested. The FET has the unique feature that either a positive or negative gate-source temperature coefficient can be obtained, dependent on the bias conditions. (2) Accordingly, in the initial experiments an effort was made to bias the FET to obtain a zero temperature coefficient. This would be most desirable, but it was found to lead to undesirably high noise levels. In the final design the operating bias was selected for minimum noise since temperature compensation could be provided elsewhere in the circuit.

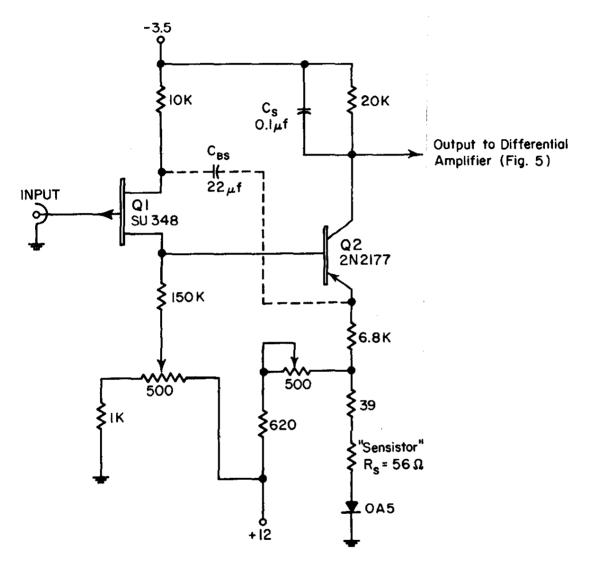

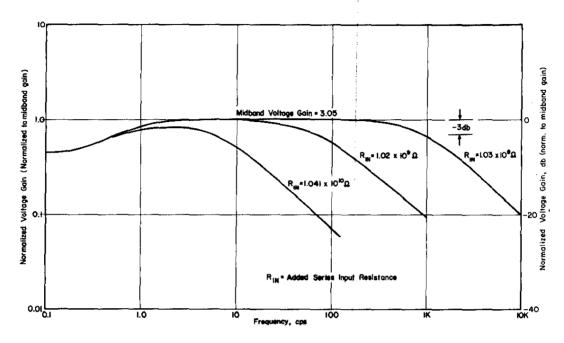

#### FET Input Circuit

The input circuit (Figure 1) consists of an FET source follower used to drive a PNP transistor, 2N2177. The circuit has a DC gain of approximately 1.25.

Measurement of the DC input impedance of a device with such a high impedance is difficult because of unavoidable stray leakage currents in the test setup; however, some measurements were made to approximate the value. Resistors of known value were inserted in series with the circuit input, and gain-frequency curves were plotted. The 3-db point on the bandwidth curve occurred when the AC impedance was equal to the series input resistor value. A simple calculation gave input capacitance. The frequency roll-off of the circuit without series input resistance was 150 kc. "Bootstrapping" the circuit (connecting  $C_{\rm BS}$  as shown in Figure 1) decreased the effective input capacitance. The bootstrapping applied positive feedback to the FET drain, reducing the gate-drain capacitance. Gain-frequency curves with and without bootstrapping are shown on Figures 2 and 3.

FIG. 1 FET INPUT CIRCUIT - SCHEMATIC

FIG. 2 BANDWIDTH CURVES - AMPLIFIER BOOTSTRAPPED

FIG. 3 BANDWIDTH CURVES - AMPLIFIER NOT BOOTSTRAPPED

The following values of input capacitance were calculated from the curves.

TABLE I

Input Capacitance Values

| Circuit<br>Conditions | AC Input<br>Impedance,<br>ohms                   | Frequency | Calculated Input<br>Capacitance, pf |

|-----------------------|--------------------------------------------------|-----------|-------------------------------------|

| Bootstrapped          | 11.4 x 10 <sup>6</sup> 56.6 x 10 <sup>8</sup>    |           | 1.4<br>1.7                          |

| Not Bootstrapped      | 11.4 x 10 <sup>6</sup><br>56.6 x 10 <sup>8</sup> |           | 2.1<br>2.4                          |

The DC input resistance was approximated using the same series input resistor method. When the value of series resistance approached the value of FET input resistance, the DC gain of the circuit was reduced. The data revealed that the input resistance was 500-1000 gigaohms (10° ohms).

Figure 4 shows the graphs of impedance vs. frequency. The final version of the operational amplifier tested in this report was not bootstrapped.

FIG. 4 IMPEDANCE VS. FREQUENCY - FET INPUT CIRCUITS

#### Differential Amplifier

The gain portion of the amplifier consists of three differential amplifier stages (Figure 5), with differential transistors for low drift. (A differential transistor consists of a matched pair of transistors constructed in a common can.) The overall differential DC gain was 3700. The roll-off frequency was 65 kc. The differential amplifier output has an overall temperature drift of 6  $\mu v/^{\circ} C$ , referred to the input.

FIG. 5 DIFFERENTIAL AMPLIFIER - SCHEMATIC

#### Operational Amplifier

The integration of the FET input circuit and the differential gain stages (Figures 1 and 5) completes the operational amplifier. The open loop DC gain was 2400, rolling off at 60 kc. This resulted in an unstable closed loop operation since the gain was well above unity when  $180^{\circ}$  phase shift occurred in the amplifier; therefore, frequency shaping was applied in the FET circuit with a 0.1- $\mu$ f capacitor across the 2N2177 load resistor (C<sub>S</sub>, Figure 1). The amplifier was then stable with 100% negative feedback. Curves for open loop and closed loop conditions are shown in Figure 6. The circuit was cycled in a temperature test oven;

FIG. 6 GAIN - FREQUENCY CURVES - OPERATIONAL AMPLIFIER

total drift was 1 mv between 20 and 32°C, referred to the input, as shown in Figure 7. The overall performance of the amplifier is summarized in Table II. This performance is regarded as quite satisfactory for laboratory-type operation.

FIG. 7 VOLTAGE DRIFT OF OPERATIONAL AMPLIFIER

## TABLE II Operational Amplifier Specifications

| DC voltage gain           | 2400 (68 db)                                                          |

|---------------------------|-----------------------------------------------------------------------|

| Bandwidth                 | 100 kc                                                                |

| Input resistance          | 500 gigaohms                                                          |

| Input capacitance         | 2.3 pf                                                                |

| Output impedance          | 600 ohms                                                              |

| Output voltage            | ±1.5 volts                                                            |

| Input current             | 7 x 10 <sup>-13</sup> amp @ 23°C<br>5 x 10 <sup>-12</sup> amp @ 40°C  |

| Voltage drift             | 1 mv total deviation referred to input between 20 and 32°C (Figure 7) |

| Warm-up drift             | -50 my in 3 hr at output                                              |

| Output waveform rise time | 3 ms                                                                  |

#### **FUTURE WORK**

Since the start of this work a number of semiconductor manufacturers have introduced a metal oxide field-effect transistor (MOS FET), which uses an insulated gate and has a much higher input impedance than any other FET now available. Impedance ranges are 10<sup>15</sup> - 10<sup>18</sup> ohms. The development of the MOS FET is a breakthrough for so lid-state circuit design. Immediate plans are to design an improved operational amplifier with MOS FETs and to use the new amplifier in logarithmic converter circuit.

#### **REFERENCES**

- 1. J. F. Gibbons and H. S. Horn. "A Circuit with Logarithmic Transfer Response Over 9 Decades." IEEE Transactions of the Circuit Theory Group, Volume CT-11, Number 3, September 1964.

- 2. "Biasing UNIFETs to Give Zero DC Drift." Application Note, Siliconix Incorporated, Sunnyvale, Calif., July 1963.

Simplified Construction Diagram

Circuit Symbol